Verilog, VHDL, SystemC et tous les HDL en général, permettent de modéliser un système, c'est-à-dire d'en donner un modèle abstrait, en laissant de côté certains détails.

Suivant le type des détails précisés ou omis, on distingue plusieurs types de modélisation, appelées aussi modèles ou vues :

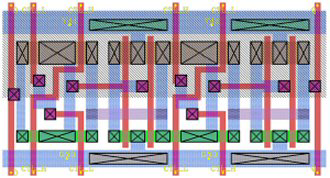

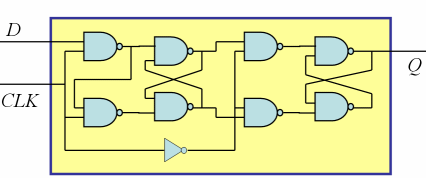

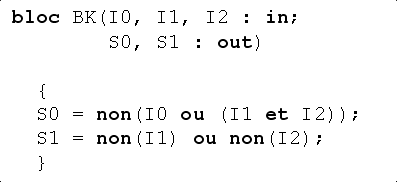

Pour une bascule D, les différentes représentations seraient, par exemple :

Chacun de ces modèles peut être plus ou moins raffiné, selon la finesse des détails qu'on y présente.

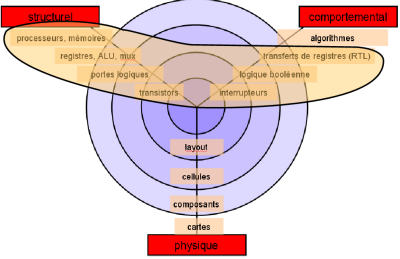

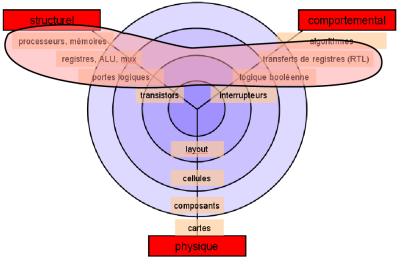

On représente souvent ces trois types de modèles et leur degrés de finesse selon un diagramme dit "en Y" :

Bien sûr, en pratiques, ces différents

modèles sont souvent

mélangés.

On peut

décrire une partie d'un système sous forme

physique (j'ai

un microprocesseur, dont le boîtier carré de 20mm

de côté),

une partie en comportemental (l'ALU

effectue une addition de tel et tel registre si l'instruction commence

par

"100", sinon elle en fait la soustraction ),

une partie en structurel (le

cache est une SRAM, formée

de points SRAM, eux-mêmes formés de transistors

agencés de

telle et telle façon),

voire même donner plusieurs modèles d'une

même partie.

De plus, la frontière entre les différentes descriptions sont souvent floues (sans compter les abus de langages). Par exemple, une représentation comportementale sous forme d'équation booléenne (S = A XOR B XOR C) suggère une implémentation directe sous forme de portes logiques (ici deux portes XOR). Cette équation peut donc être vue

Les abus de langage font aussi qu'on présente souvent le plus haut niveau d'abstraction d'un système comme comportemental même s'il est structurel. Et bien souvent on parle de RTL à la place de comportemental et vice-versa, alors que le RTL n'est qu'un de ses niveaux de finesse...

Bref, les frontières entre niveaux sont floues, celles entre les modèles aussi. Pour plus de précisions, on pourra se rapporter à [Armstrong] VHDL design : Representation and synthesis.

Verilog, VHDL et SystemC permettent de représenter des systèmes sous forme structurelle ou comportementale, dans la majorité des degrés de finesse. Par contre, ils ne savent pas décrire la partie physique.

De plus, les habitudes de travail font que chaque niveau n'est pas conçu par les mêmes personnes, et chaque population a ses propres habitudes. Par exemple, la description de plus haut niveau d'une chaîne de traitement UMTS sera faite par des gens du traitement du signal, qui représentent généralement leurs algorithmes en C ou en Matlab. C'est le niveau du dessous qui sera traité par les électroniciens, qui travailleront alors en Verilog, VHDL ou SystemC.

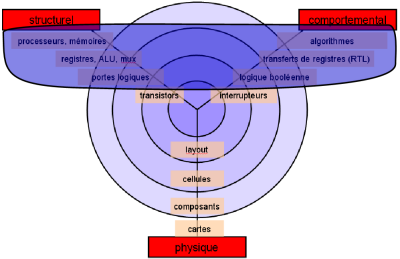

Le diagramme suivant représente les différents modèles représentés traditionnellement en Verilog, VHDL et SystemC :

Trois niveaux / modèles sont plus particulièrement utilisés en Verilog :

Ces trois descriptions sont utilisées conjointement, souvent à l'intérieur d'un même fichier, selon la forme la plus simple / pratique pour le concepteur.

Le passage d'une vue à l'autre est appelée synthèse. Il en existe donc deux types :

En pratique, le terme synthèse est utlisé pour le passage d'une quelconque vue comportementale ou d'une vue structurelle de niveau élevé (registres / ALU /mux et au dessus) à une vue structurelle en portes logiques, c'est-à-dire d'une représentation relativement abstraite, telle qu'elle est utilisée par les concepteurs, à une représentation bas niveau utilisable pour le placement-routage. C'est donc un mélange de synthèse logique et éventuellement de raffinement d'une vue structurelle.

Il existe trois types de modélisation d'un système :

Chaque type de vue a plusieurs niveaux de raffinement, selon la finesse des détails présentés.

Un circuit est généralement