Pour simuler ou effectuer la synthèse logique d'un modèle VHDL, il faut d'abord le compiler (on dit analyser pour le VHDL) . Les résultats d'analyse sont stockés dans une bibliothèque. Avant analyse Il faut donc préciser au compilateur la bibliothèque dans laquelle sera rangé le résultat. Dans un programme VHDL, on peut ainsi faire référence à un objet préalablement analysé en prenant soin de préciser dans quelle bibliothèque se trouve l'objet.

Une fois la compilation terminée, il faut effectuer l'édition de lien (on parle d'élaboration pour le VHDL). L'élaboration s'effectue sur la description structurelle de plus haut niveau hierarchique (l'équivalent du schéma au plus haut niveau).

La simulation peut alors s'effectuer sur le résultat de l'élaboration (rangé dans la bibliothèque spécifiée avant élaboration).

L'analyse d'un modèle VHDL peut s'effectuer sur des parties du code ou "unités de compilation". Il existe 5 types d'unités de compilation :

L'entité et l'architecture sont des unités de compilation obligatoires pour décrire un modèle. Les autres unités sont optionnelles mais quasiment indispensables pour concevoir des gros circuits nécessitant une méthode de conception efficace.

Une unité de compilation doit être écrite dans le même fichier et un même fichier peut contenir plusieurs unités de compilation.

L'objectif de ce chapitre est de vous présenter les conventions lexicales de VHDL, les bibliothèques et les unités de compilation (à part la configuration qui sera vue dans le chapitre sur le VHDL structurel)

Les conventions lexicales de vhdl sont les mêmes que celles utilisées en C. Un code vhdl est composé d'une suite d'éléments :

VHDL est insensible

à la casse. Un mot en majuscule est identique à

un mot en

minuscule. Il est cependant conseillé d'avoir des

règles

d'écriture cohérentes. Par exemple, les mots

reservés du langage peuvent être en majuscule et

les

autres mots en minuscule.

Les commentaires doivent

être inclus dans le code, pour augmenter la

lisibilité et la

documentation. Ils commencent par 2 tirets (--) en se terminent en fin

de ligne

Il est impératif de documenter vos codes, à l'école comme en entreprise.

Ce sont les noms de variables, de signaux, de fonctions, ...

Ce sont des valeurs explicites :

Les bibliothèques permettent à plusieurs concepteurs de travailler ensemble sur le même projet et rendent le langage indépendant du système d’exploitation de la machine hôte.

La création de la bibliothèque ne fait pas partie du langage VHDL Chaque outil VHDL a donc ses propres règles de création.. Par exemple avec le simulateur ModeSim il faut créer la bibliothèque avec cette commande :

vlib BIB

L'accès à la bibliothèque fait partie du langage VHDL. Pour accéder à la bibliothèque BIB il est nécessaire de la déclarer :

library BIB;

La bibliothèque par défaut est WORK . WORK est aussi le nom symbolique de la bibliothèque dans laquelle sont stockés les résultats. La bibliothèque STD est une bibliothèque standard fournie avec le langage , elle contient des définitions des types et des fonctions de base (integer, BIT, BOOLEAN,...) dans le paquetage STANDARD et des fonctions sur les caractères dans le paquetage TEXTIO.

Par défaut, les bibliothèques STD et WORK n’ont pas besoin d’être déclarées pour être utilisables. Tout se passe comme si un programme VHDL commençait toujours par :

library STD;

library WORK;

Il

est très pratique d'utiliser les paquetages

des bibliothèques ce qui permet d'utiliser des

objets

(constantes, fonctions, composants,...) qui peuvent être

définis dans une bibliothèque

différente de celle

en cours. C'est le cas des bibliothèques standards comme l'IEEE qui

définit des types et objets

normalisés compris par les outils de

synthèse.

Pour

utiliser le contenu d’un paquetage, il faut

déclarer la bibliothèque dans laquelle il se

trouve (sauf, éventuellement,

si c’est WORK)

et le paquetage :

use BIBLIOTHEQUE.PAQUETAGE.all;

ou, si l’on ne veut pas utiliser tout le paquetage mais un seul objet :

use BIBLIOTHEQUE.PAQUETAGE.OBJET;

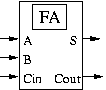

L'entité est la description de l'interface du circuit . Elle correspond au symbole dans les représentations schématiques :

symbole de l'additionneur 1 bit

L'entité précise :

library ieee; |

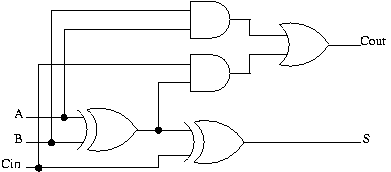

L'architecture est la description interne du circuit. Elle est toujours associée à une entité. Une même entité peut avoir plusieurs architecture. Le mécanisme de configuration (décrit dans le VHDL structurel) permet d'indiquer l'architecture rattachée à une entité. L'exemple suivant montre un schéma de l'additionneur 1 bit fa et 2 architectures possibles écrites en VHDL :

architecture arc1 of fa is |

architecture arc2 of fa is |

VHDL est un langage très déclaratif qui permet au compilateur d'effectuer des vérifications poussées et fiabiliser ainsi l'écriture d'un modèle.

Dans une architecture il est nécessaire de déclarer les objets utilisés et leur type avant la zone décrivant l'architecture (le corps de l'architecture situé entre begin ... end ).

Parmi les objets très utilisés, figurent les composants (correspondent effectivement aux composants dont on a besoin dans l'architecture pour une description structurelle) et les signaux (equipotentielles reliant les instances de composants et les instructions "concurrentes" et).

Les ports déclarés dans l'entité sont des signaux utilisables dans l'architecture, il ne faut pas les redéclarer.

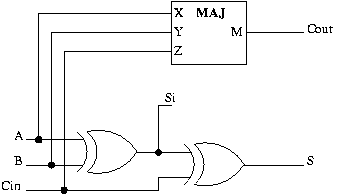

L'exemple ci-dessous illustre l'architecture d'un additionneur 1 bit avec les signaux A, B , Cin (qui sont des ports donc des signaux implicites) , le signal Si et le composant MAJ .

Le schéma équivalent de l'additionneur 1 bit peut être le suivant avec 1 composant MAJ et 2 portes XOR qui peuvent être codées d'une façon comportementale.

Le code VHDL correspondant :

entity FA is |

Entité de l'additioneur 1 bit FA |

architecture arc3 of fa is |

La partie déclarative de l'architecture, avant le mot clé begin, permet de déclarer le signal SI et le composant MAJ. |

begin |

Dans le corps de

l'architecture (entre begin

et end)

se trouvent les 3 types d'instructions concurrentes de

VHDLqui peuvent être écrites dans n'importe quel

ordre :

Cout <= S and B car S est une sortie qui ne peut pas servir d'entrée. |

package PAQ is |

Le paquetage PAQ

est déclaré avec le mot clé package.

Des nouveaux types

type

et sous-types

subtype sont

déclarés. Dans cet exemple on déclare le type MOT qui est un vecteur de 8 bit, un type RAM qui est un tableau de MOT et un sous type MRAM qui est une RAM de 1024 MOTS. Des constantes "constant" N_BITS et REL sont déclarées. N_BITS est un entier > 0 "positive" et REL est un entier naturel "NATURAL" et est initialisée à la valeur 8. Le composant "component" BRIQUE est déclaré ici en précisnat ces ports et paramètres. La déclaration d'un composant permet son instanciation dans l'architecture de façon à effectuer une description structurelle Le sous-programme ou fonction "function" MIN est déclarée dans le paquetage. La description de la fonction ser effectuée dans le corps du paquetage. |

package body PAQ is |

Le

corps du

paquetage "package body"

permet de décrire les sous-programmes et d'initialiser les

constantes. La constante N_BITS est initialisée ici. Elle aurait pu être utilisée localement au corps du sous programme sans être visible de l'extérieur. Les fonctions peuvent être surchargées en nom ou en type. Ici 2 fonctions MIN sont décrites , l'une avec 2 entrées et l'autre avec 3 entrées utilisant celle à 2 entrées. |

Le prochain chapitre traite des types et des opérateurs de base en VHDL